# Modelization and simulation of intermittent stuck bits phenomenon

Supervisor : Frederic Wrobel Co-Supervisor : Alain Michez CNES resp. : Francoise Bezerra

#### Nguyen Tran Hoang

#### IES, Montpellier 12/02/2018

IES | Institut d'Électronique et des Systèmes UMR 5214 - CNRS - UM Université de Montpellier 860, rue Saint Priest Bâtiment 5 - CC 05001 34095 Montpellier cedex s tel +33 (0)4 67 14 37 16 fax +33 (0)4 67 54 71 34 www.ies.univ-montp2.fr

### Briefly about the subject

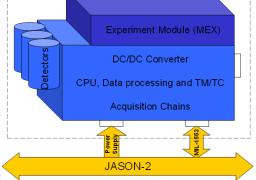

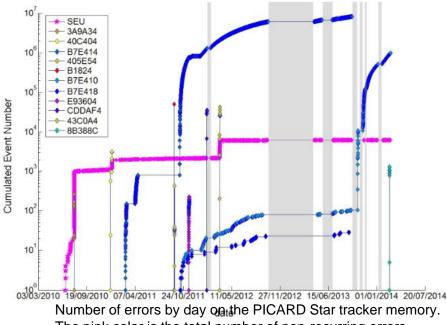

Errors appears on board CNES satellite : memory of Star Tracker on PICARD and CARMEN2/JASON2 (A.Samaras "Experimental characterization and In-flight observation of Weakened cell in SDRAM")

Previous studies by Axel Rodrigues: Reproduce these errors at ground level Characterize the behavior of faulty SDRAM cells Study the mechanism and origin of phenomenon Simulation with TCAD software (ecorce)

My work:

Modelization and simulation of the phenomenon

#### CARMEN-2 aboard JASON-2

IES | Institut d'Électronique et des Systèmes UMR 5214 - CNRS - UM Université de Montpellier 860, rue Saint Priest Bâtiment 5 - CC 05001 34095 Montpellier cedex 5 tel +33 (0)4 67 14 37 16 fax +33 (0)4 67 54 71 34 www.ies.univ-montp2.fr

### **SDRAM technology**

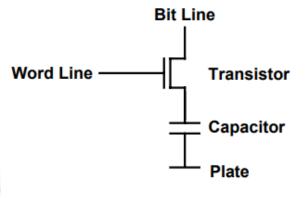

SDRAM - Synchronous Dynamic Random Access Memory

Characteristics:

#### Volatile

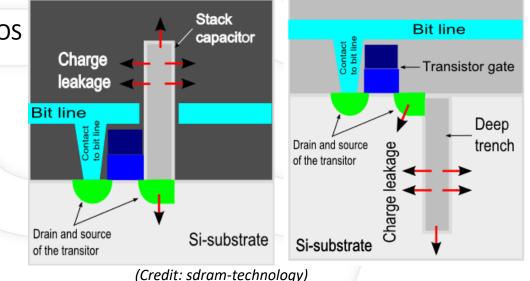

SDRAM cell is made up of a single MOS transistor and a storage capacitor Need refresh to keep charges Susceptible with radiation effects

Source: ICE, "Memory 1997" 19941

#### 1T/1C DRAM cell

### **Intermittent Stuck Bits - ISBs**

- Observation repeated errors in memory of PICARD Star tracker and in CARMEN2 experiment.

- **Characteristics:** Localized : happen on preferential address Intermittent : the errors disappear after a period of time

Persistent : restart devices do not fix the err

- $\Rightarrow$  Not SEU or Stuck bits

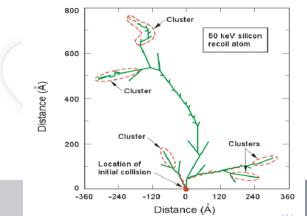

- Strongly because:

Displacement damage cluster inside the depletion region

[L. D. Edmonds and L. Z. Scheick "Physical Mechanisms of Ion-Induced Stuck Bits in the Hyundai 16M 4 SDRAM "]

The pink color is the total number of non-recurring errors

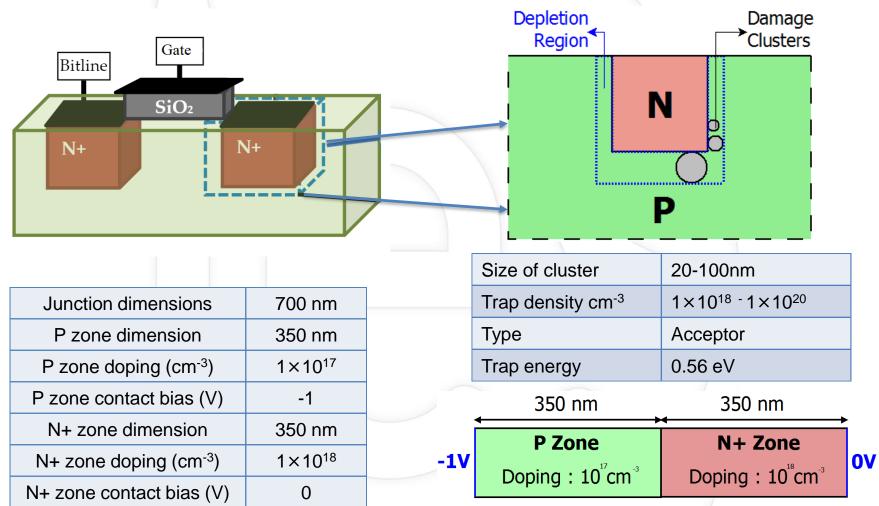

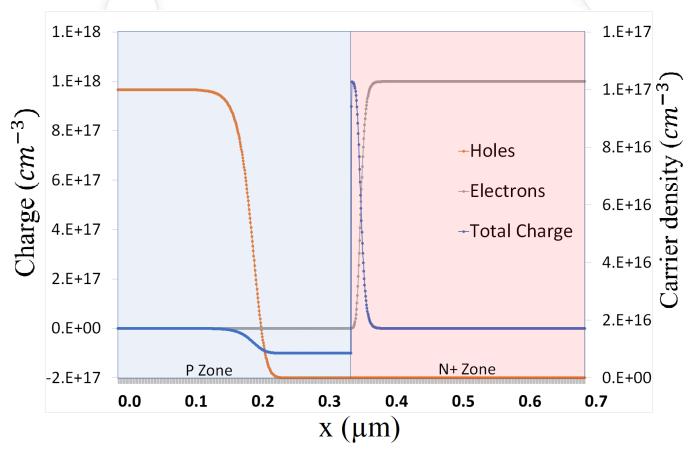

### **PN Junction simulation**

### **Pristine device**

Consider discharge as RC circuit Capacitance of 20fF – 40 fF : 1700 s retention time

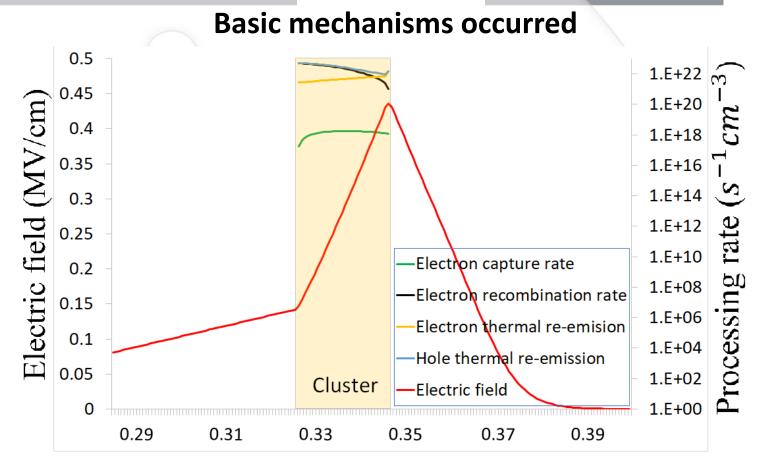

Carriers are generated by the following process : Acceptor states thermally emit holes, creating trapped electrons. A part of generated holes recombine with the trapped electrons. The most part of remaining electrons is thermally reemitted

IES | Institut d'Électronique et des Systèmes

### **Simulation** Result

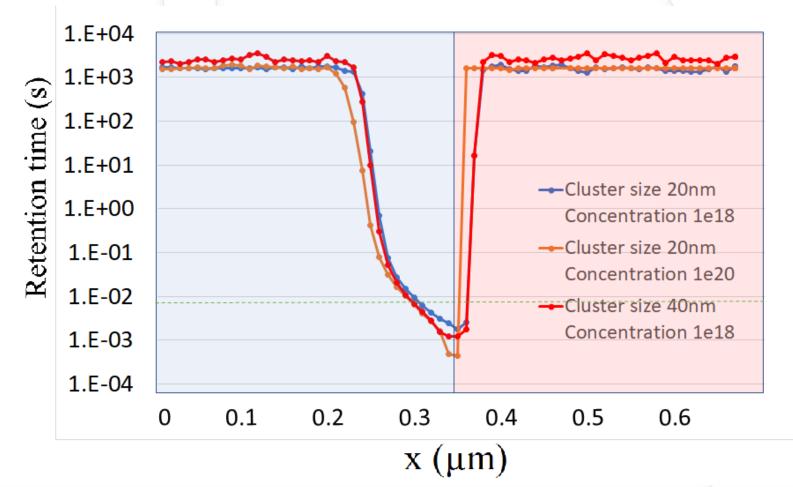

Cluster position and retention time with different size and density of cluster

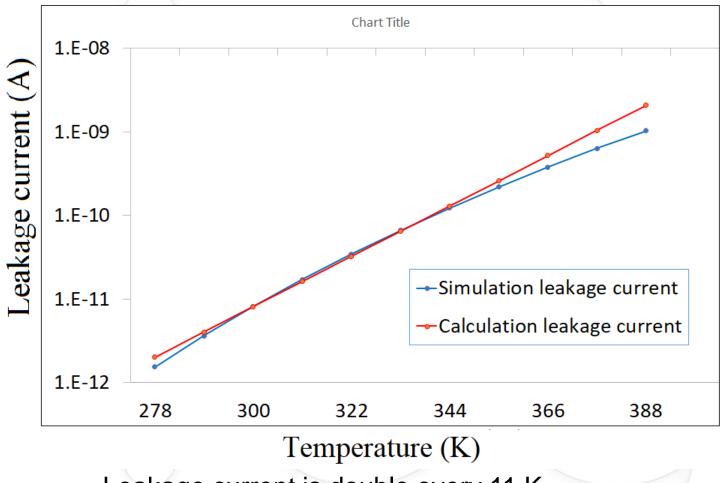

### **Temperature effect**

### Leakage current is double every 11 K

[Philippe C. Adell et.al "An Approach to Single Event Testing of SDRAMs "]

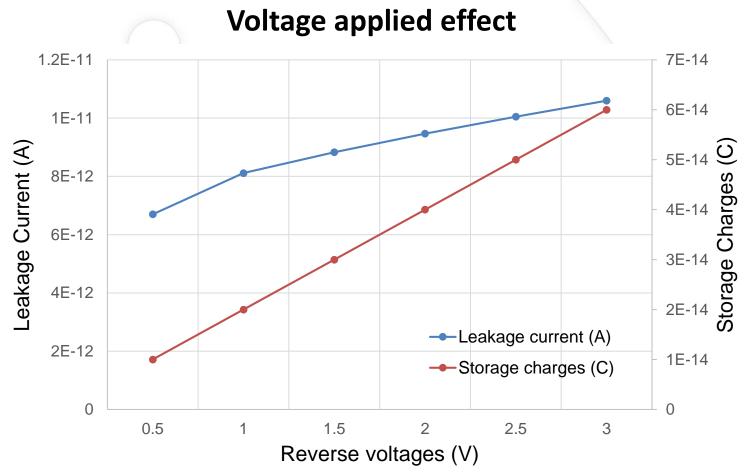

Lowering storage node voltage will increase the drop of retention time. Increasing storage node voltage, decreases the drop of retention time created.

## What's next ?

- Simulation on the total DRAM cell including capacitor; in 2D with cluster implementation

- Study the phenomenon on different trapping/detrapping energy level (previous at 0.56ev), and on different temperature.

- Building different models of displacement damage cluster (previous Gossick model) with time dependence configuration.

- Experiment with devices under beam for functional test, retention time measurement. Examination annealing effect and temperature effect.

# Back up - memory Technology

EEPROM Flash Other SRAM DRAM

Persistent values, Great capacity, lower power consumption Slower access times, throughput

Apps: start-up memory, persistent storage

Values are not persistent, Lower capacity Increased power dissipation Fast access times, throughput

Volatile

Apps: run-time memory, buffering

Variations of the 6T cross-coupled inverters with buffers Self-reinforcing nature improves SEE performance SEFI modes not as varied and often not as complex